Active-HDL

2011-09-04

Suns & Moon Laboratory

ファイル

| *.aws | workspace |

| *.adf | designe |

| *.LIB | library |

| *.awf | wafeform |

シミュレーションをやってみる

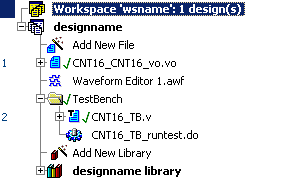

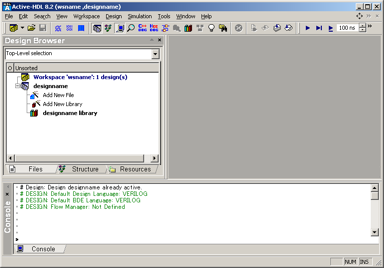

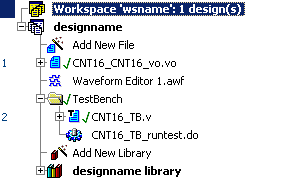

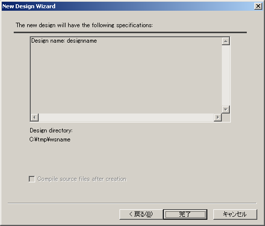

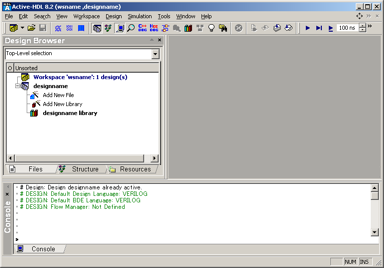

最終的にはこうなる

★無料ライセンスだと1workspaceに1デザイン。でもvやテストベンチは複数おけるので、まぁ困らない。

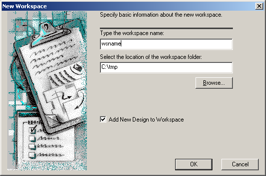

| workspace name | 指定した名称のフォルダが生成される |

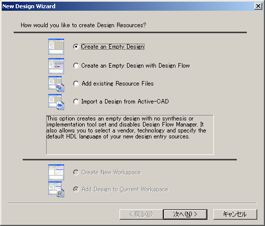

| design name | 指定した名称のライブラリが生成される |

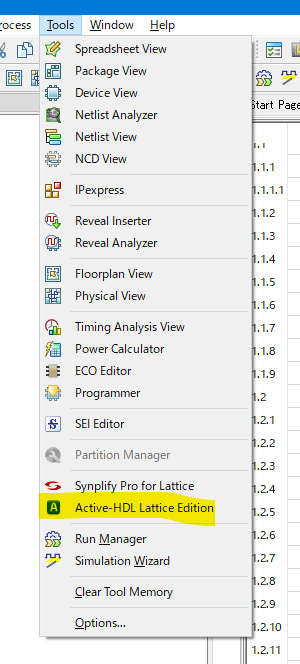

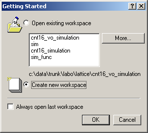

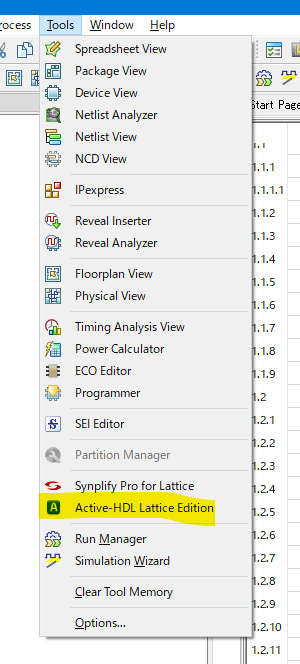

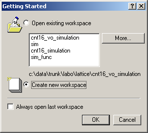

起動

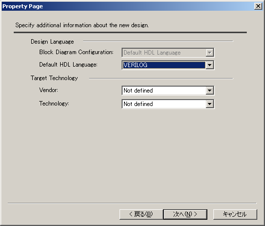

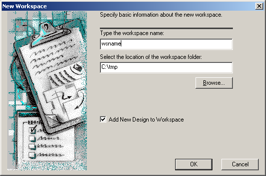

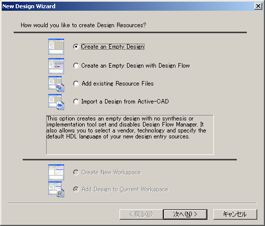

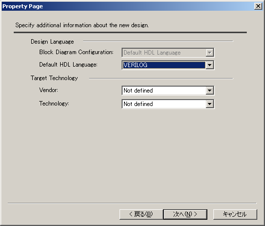

初期設定

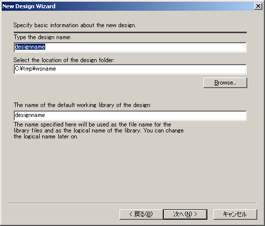

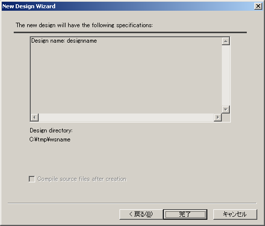

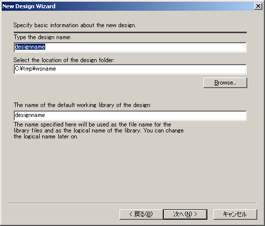

workspace name

workspace name

design name

design name

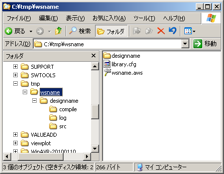

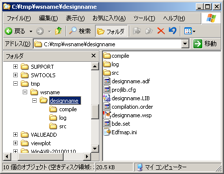

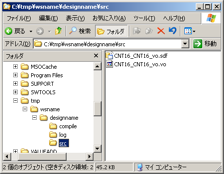

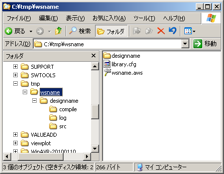

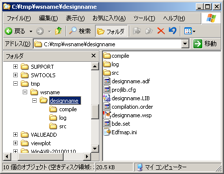

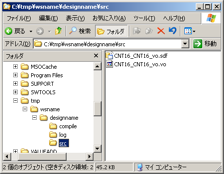

初期設定後のフォルダ構成

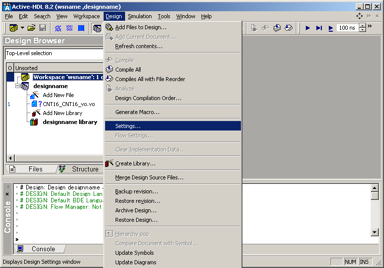

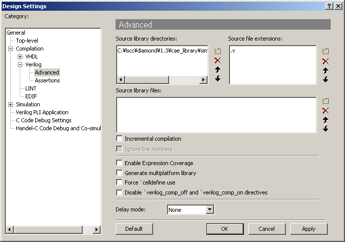

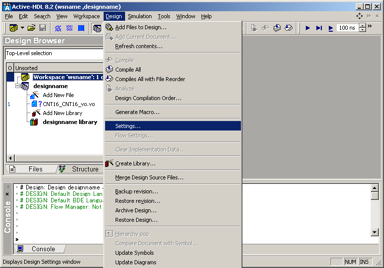

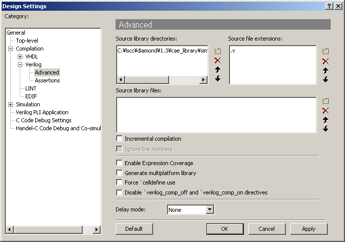

ライブラリ設定

今回はLatticeで生成したvoをシミュレーションしたいので、Latticeのライブラリパスを設定する。

C:\lscc\diamond\1.3\cae_library\simulation\verilog\machxo2

パスと拡張子を設定する

パスと拡張子を設定する

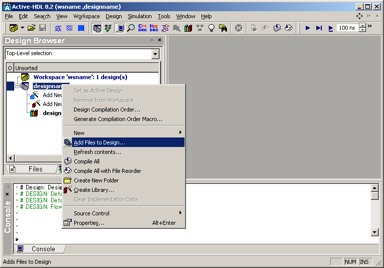

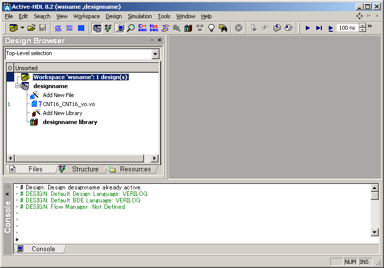

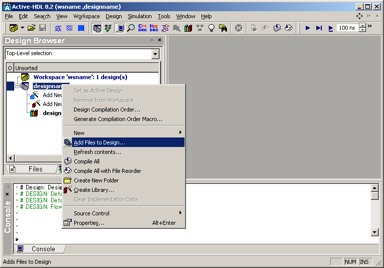

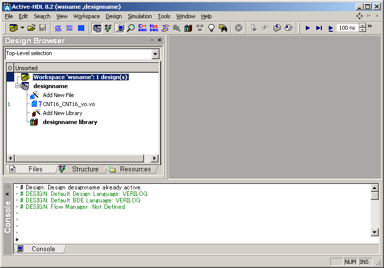

デザインを追加

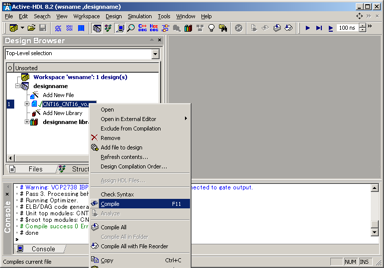

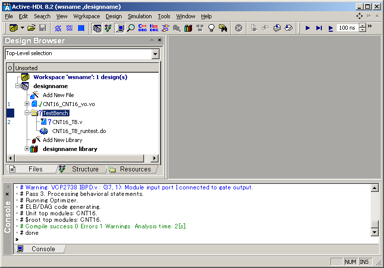

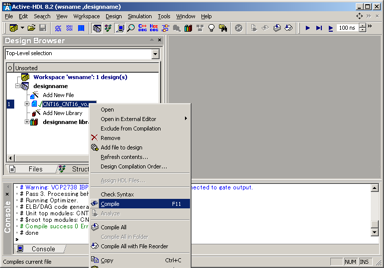

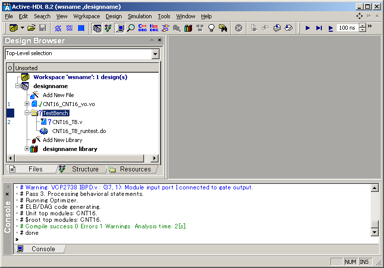

デザインのコンパイル

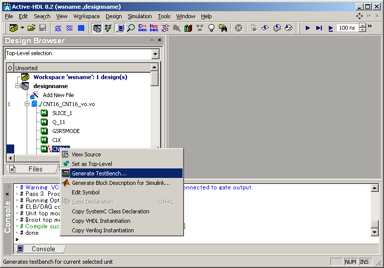

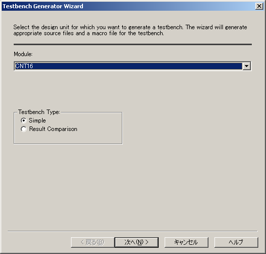

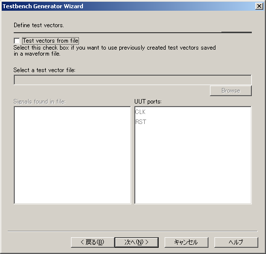

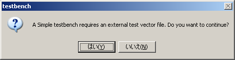

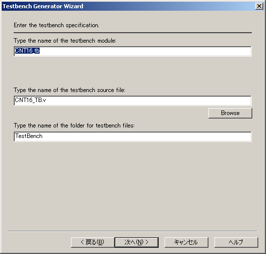

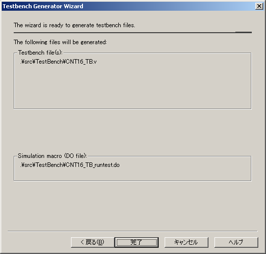

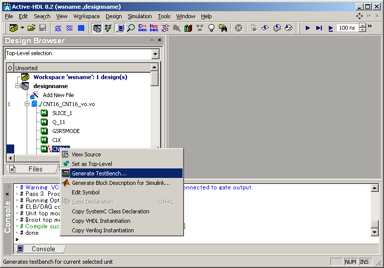

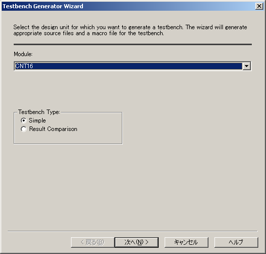

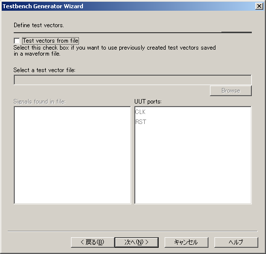

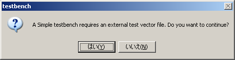

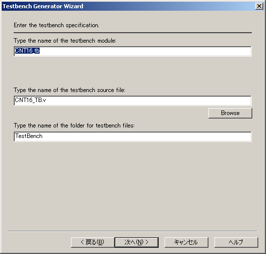

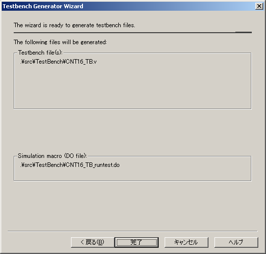

テストベンチの生成

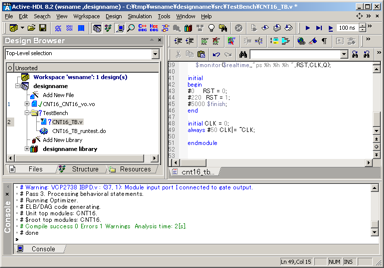

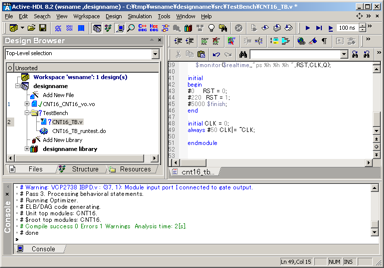

テストベンチにテスト記述

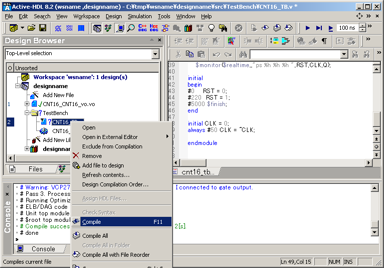

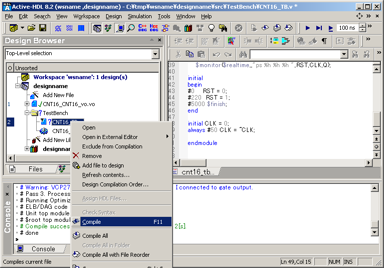

テストベンチコンパイル

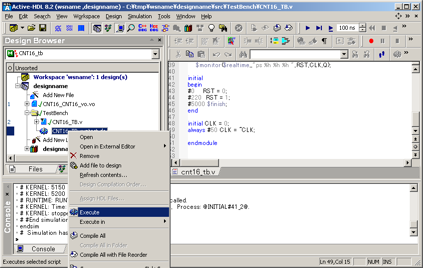

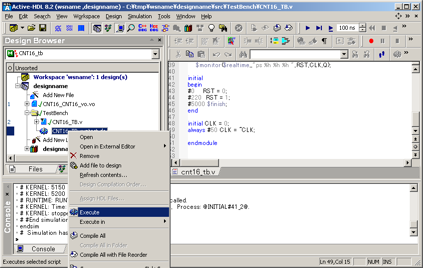

テストベンチ実行

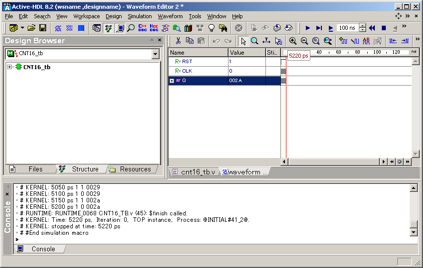

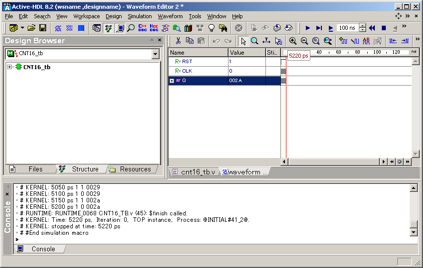

波形に信号追加

Design Browser → Hierachy → モジュール選択 →信号選択→右クリックメニューから Add To Waveform

menu→Simulation→Restart Simulation→Run

シミュレーション終了

テストベンチ

例

`timescale 1ps / 1ps

module D8E_tb;

//Parameters declaration:

defparam UUT.width = 8;

parameter width = 8;

//Internal signals declarations:

reg CLK;

reg ENB;

reg [width-1:0]DI;

wire [width-1:0]DO;

// Unit Under Test port map

D8E UUT (

.CLK(CLK),

.ENB(ENB),

.DI(DI),

.DO(DO));

initial

$monitor($realtime,,"ps %h %h %h %h ",CLK,ENB,DI,DO);

//================================================

// clock generator

//================================================

initial CLK <= 1;

always #100 CLK <= ~CLK;

//================================================

// main flow

//================================================

initial

begin

ENB <= 0;

DI <= 0;

#200 d8e_acc(8'h00);//1

#200 d8e_acc(8'h01);//2

#200 d8e_acc(8'h02);//3

#200 d8e_acc(8'h03);//4

#200 d8e_acc(8'h04);//5

#200 d8e_acc(8'h05);//6

#200 d8e_acc(8'h06);//7

#200 d8e_acc(8'h07);//8

#200 d8e_acc(8'h08);//9

#200 d8e_acc(8'h09);//10

#200 d8e_acc(8'hF8);//11

#200 d8e_acc(8'hF9);//12

#200 d8e_acc(8'hFA);//13

#200 d8e_acc(8'hFB);//14

#200 d8e_acc(8'hFC);//15

#200 d8e_acc(8'hFD);//16

#200 d8e_acc(8'hFE);//17

#200 d8e_acc(8'hFF);//18

#200 $finish;

end

//================================================

// D8E access

//================================================

// SPI_CLK = 1MHz

task d8e_acc(

input [7:0] data

);

begin

#100 ;

#100 DI <= data;

ENB <= 1;

#200 ENB <= 0;

#200;

end

endtask

endmodule

end.

2025-12-04 11:53:02 32400

workspace name

workspace name

design name

design name

パスと拡張子を設定する

パスと拡張子を設定する