Verilogメモ

Suns & Moon Laboratory

ifdef

`define XYZ

`ifdef XYZ

`ifndef XYZ

`else

`elsif

`endif

timescale

`timescale 1ns / 10ps

1nsは#1=1nsの設定

10psはシミュレーションの最小単位時間

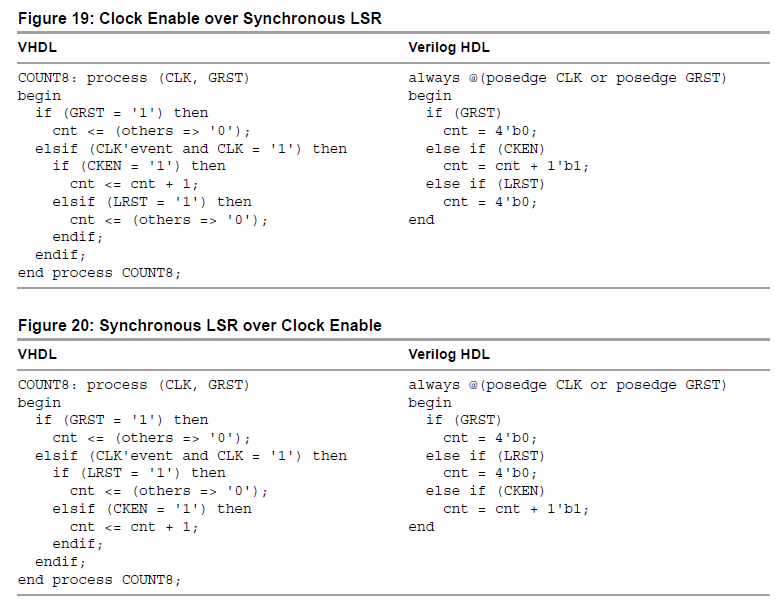

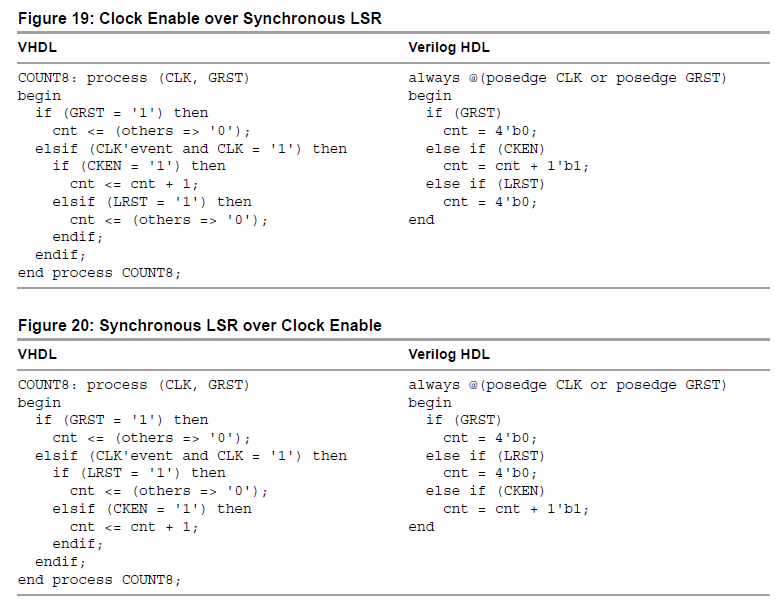

Reset(Lattice)

Lattice HDL Coding Guidelines 2012

HDLcodingguidelines.pdf

同期リセットなのでposedgeなのがポイント

P27

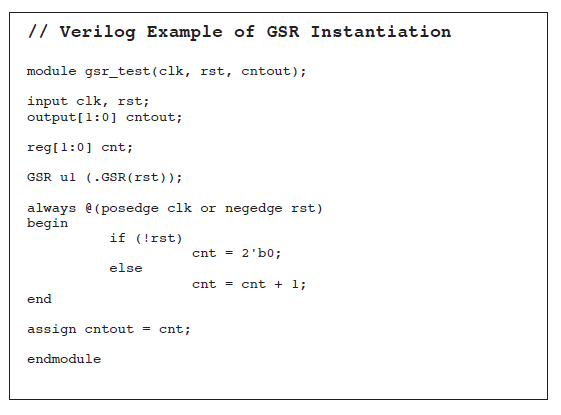

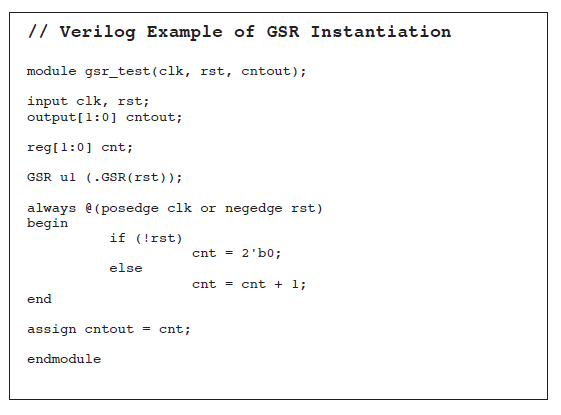

HDL Synthesis Coding Guidelines for Lattice Semiconductor FPGAs TN1008_02.1 October 2005

behaviouralVerilogSM-1.pdf

リセットはnegedgeなのがポイント

12-14

FIFO

2020-08-11作成

シミュレーション専用

module fifo_dcx (Data, WrClock, RdClock, WrEn, RdEn, Reset, Q, Empty, Full)

input wire [31:0] Data;

input wire WrClock;

input wire RdClock;

input wire WrEn;

input wire RdEn;

input wire Reset;

output reg [31:0] Q;

output wire Empty;

output wire Full;

assign Full = 1'b0;

assign AlmostEmpty = 1'b0;

assign AlmostEmpty = 1'b0;

reg [31:0] mem[0:127];//32bit width, 128 registers

reg [7:0] index_wr;

reg [7:0] index_rd;

always @(posedge WrClock or posedge Reset)begin

if(Reset)

begin

index_wr <= 0;

end

else if(WrEn)

begin

mem[index_wr] <= Data;

index_wr <= index_wr + 8'd1;

end

end

always @(posedge RdClock or posedge Reset)begin

if(Reset)

begin

Q <= 32'h00000000;

index_rd <= 0;

end

else if(RdEn)

begin

Q <= mem[index_rd];

index_rd <= index_rd + 8'd1;

end

end

assign Empty = index_wr == index_rd;

endmodule

end.

2025-12-04 11:53:02 32400